Projects  Follow @engineerswork1 Follow

Follow @engineerswork1 Follow

|

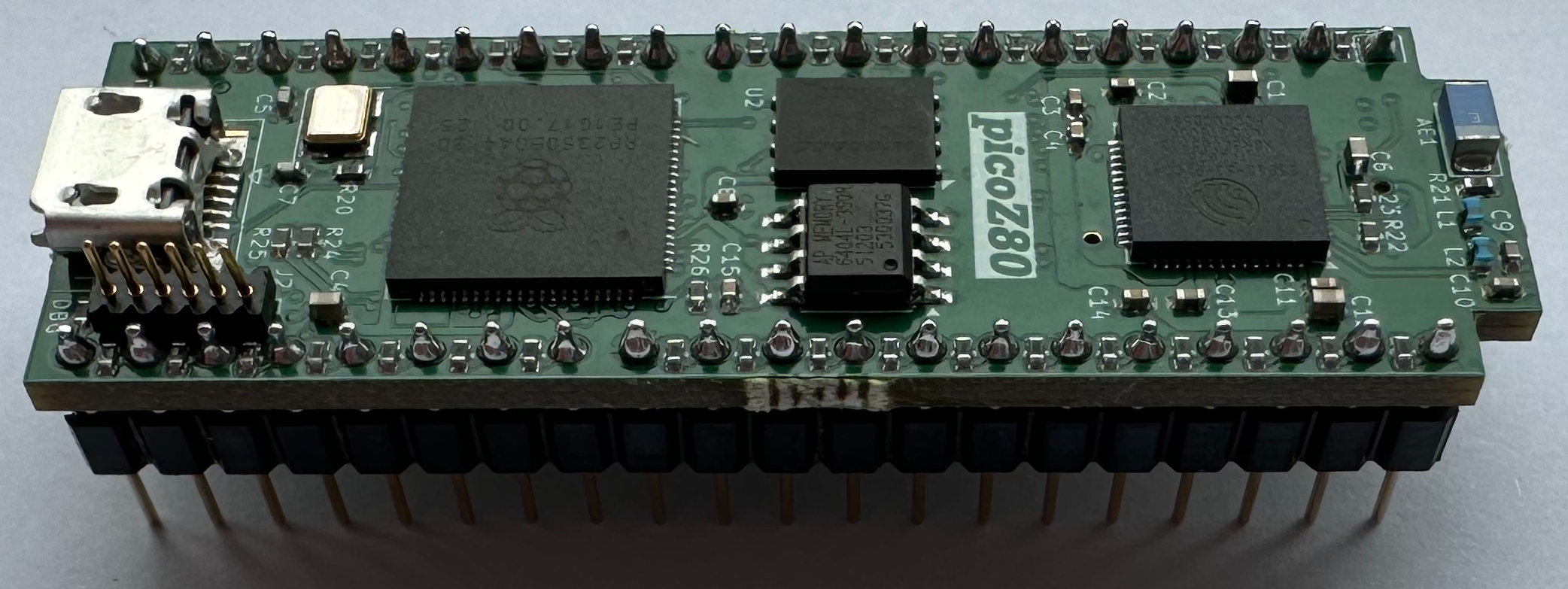

picoZ80 | RP2350 based drop-in Z80 CPU replacement with WiFi management |  |

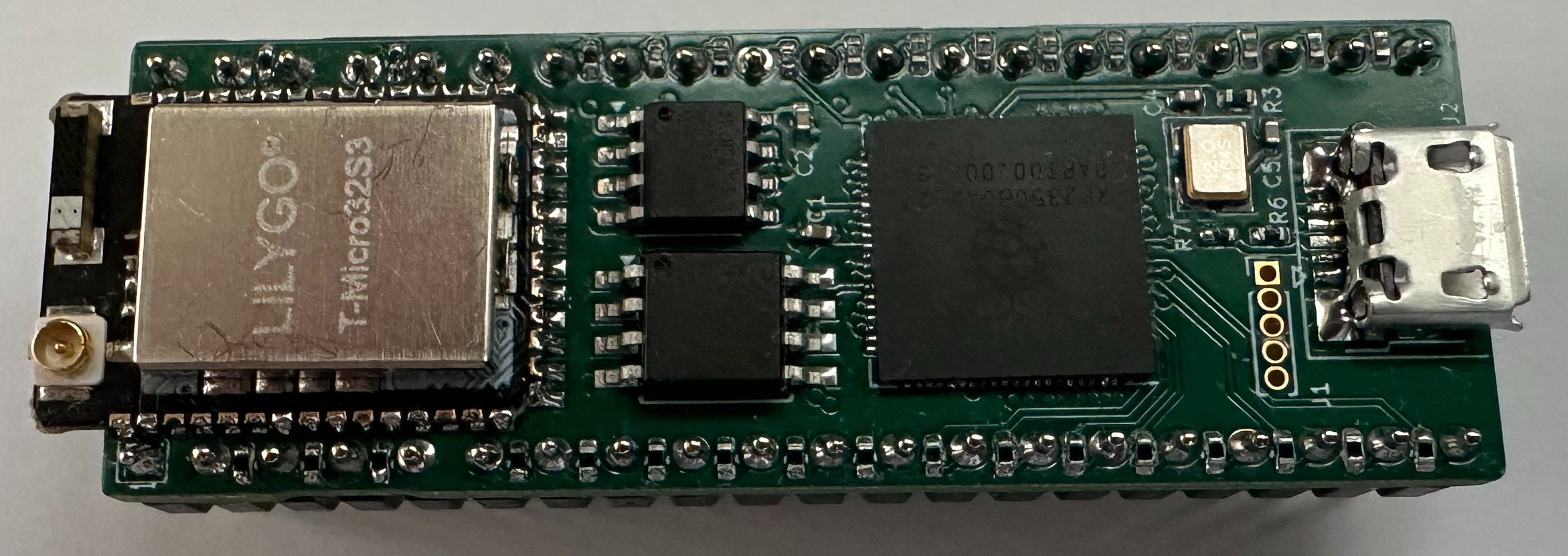

pico6502 | RP2350 based drop-in 6502 CPU replacement with WiFi management | ||

|

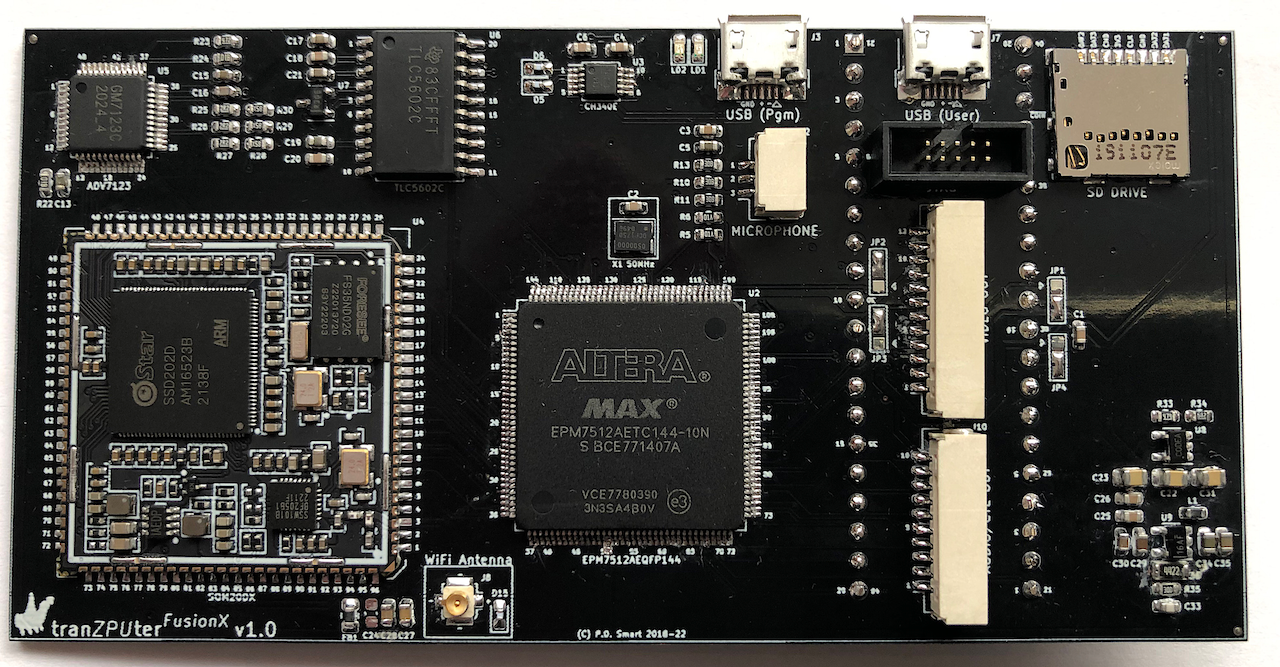

tranZPUterFusionX | Linux based in-situ CPU replacement |  |

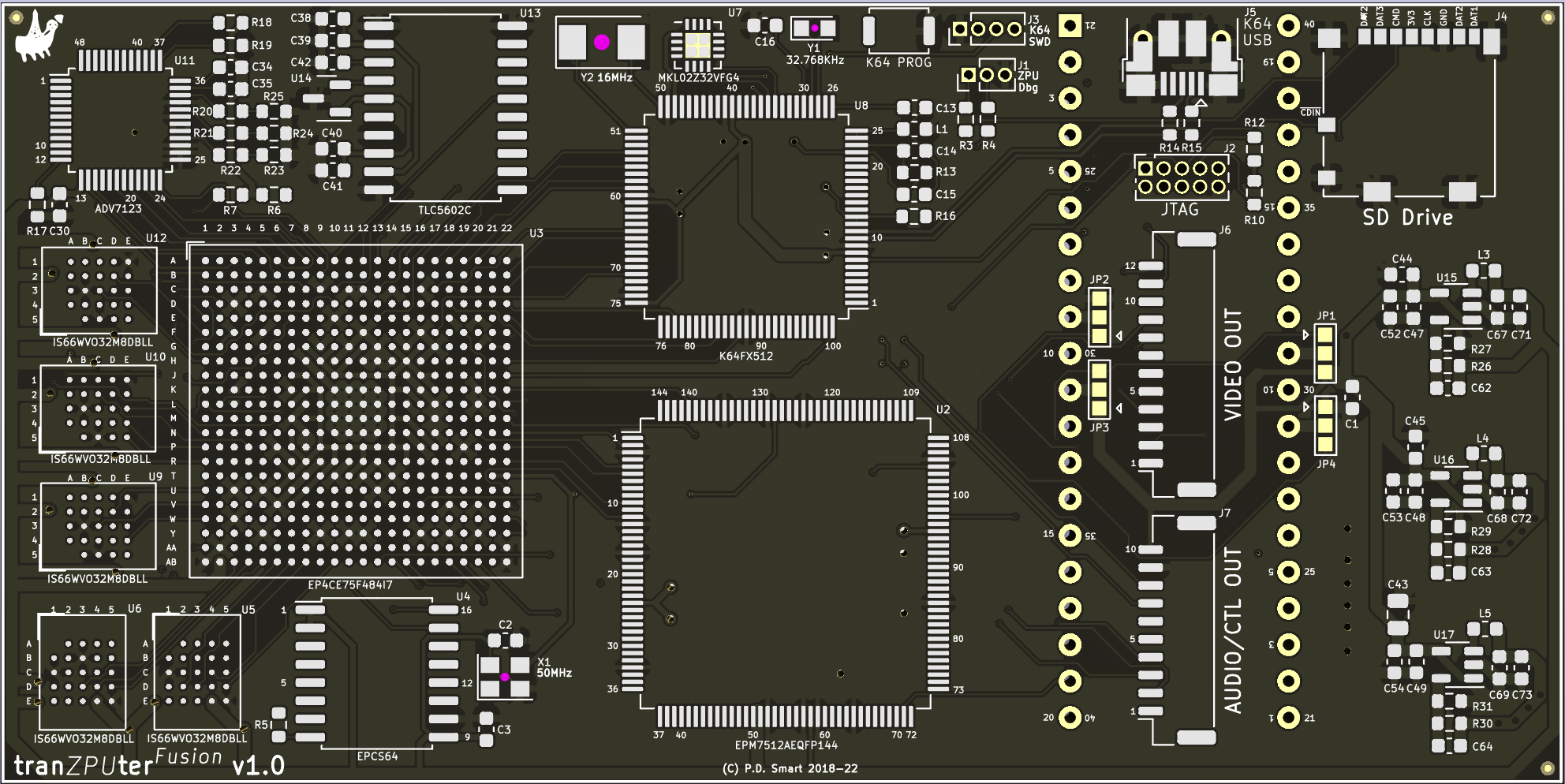

tranZPUterFusion | FPGA based in-situ CPU replacement | ||

|

SharpKey | Bluetooth/PS2 Multi Host Keyboard/Mouse Interface |  |

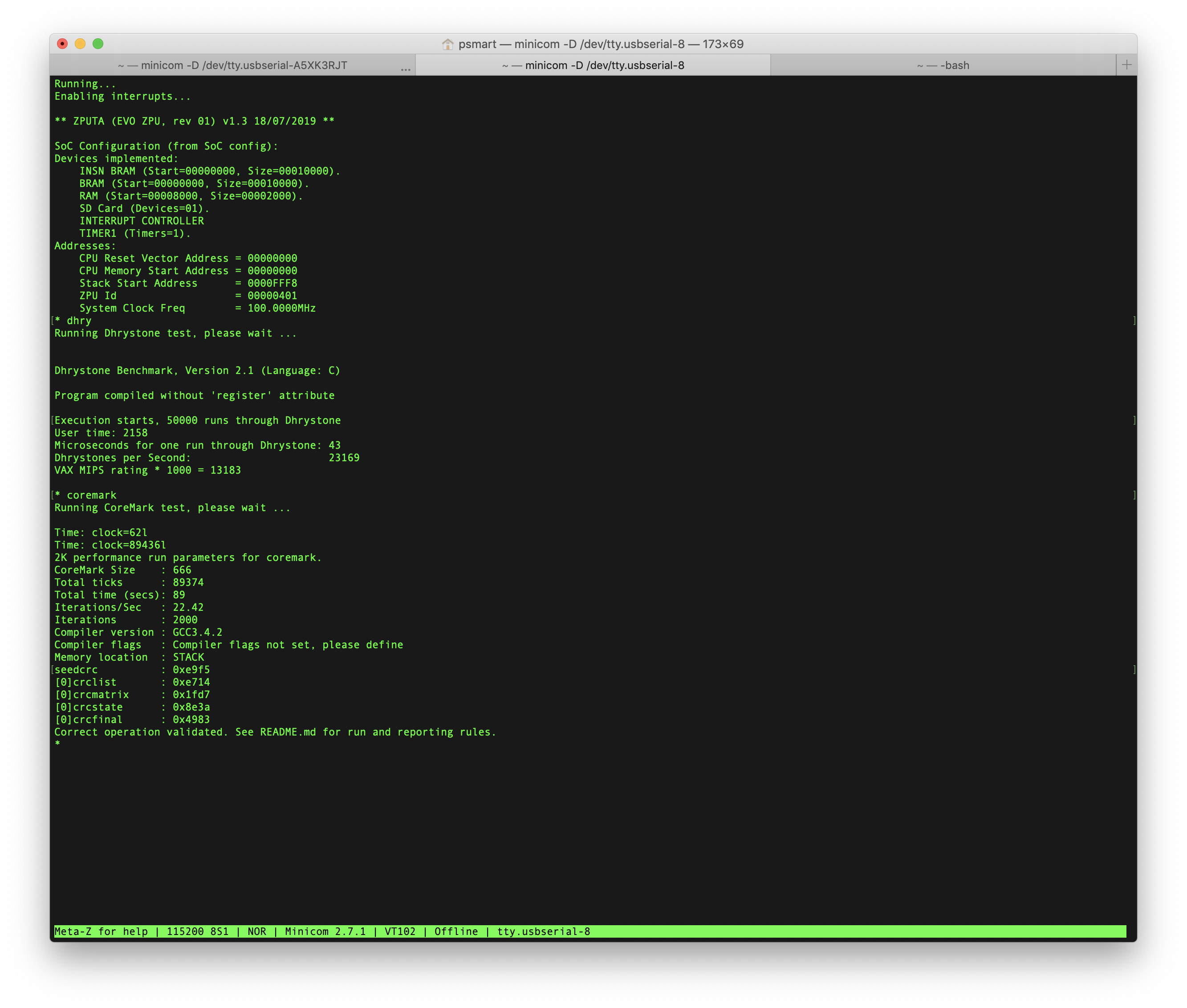

ZPU Evolution | A 32bit Processor Design for embedded products | ||

|

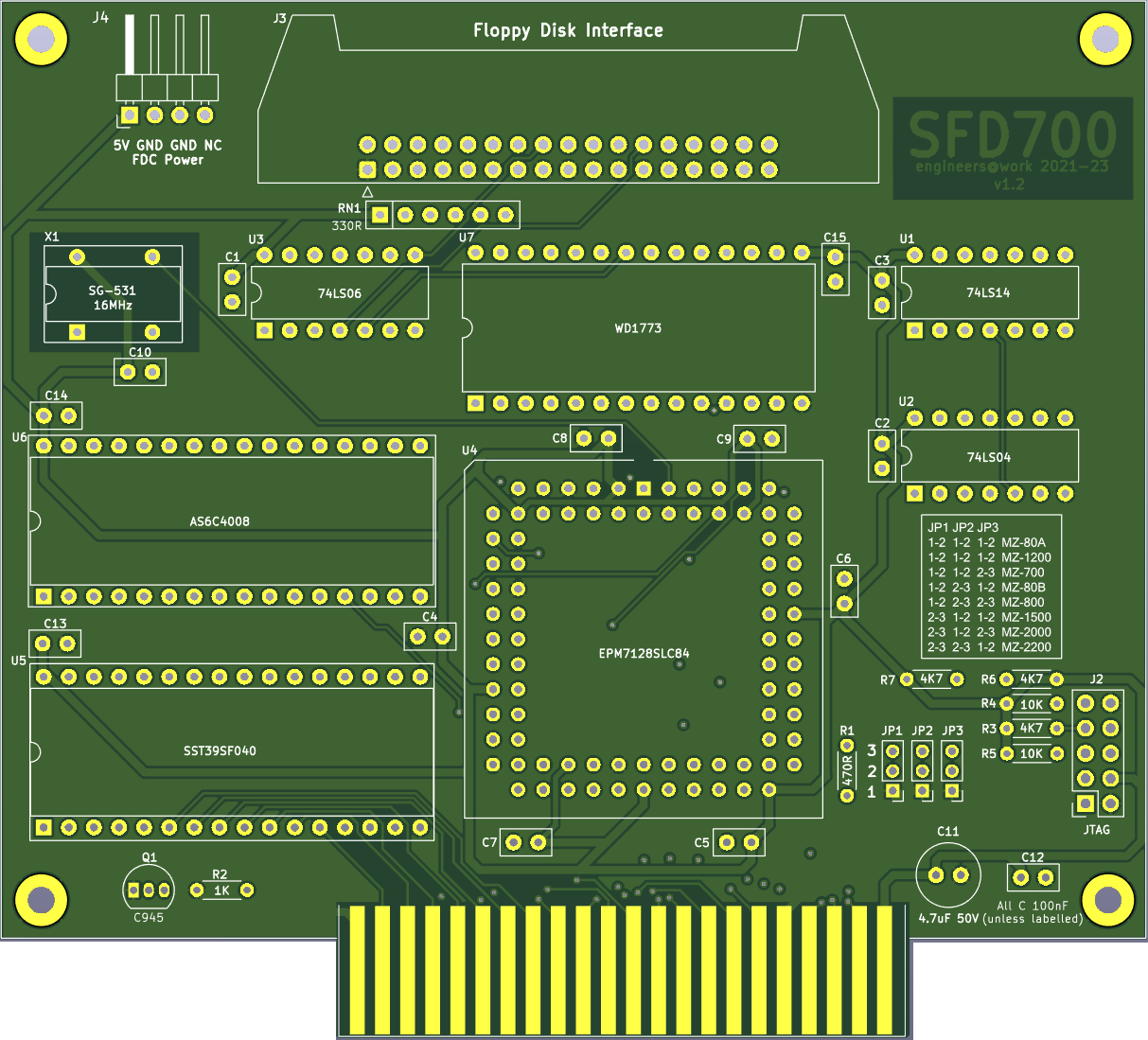

SFD-700 | Multi host (MZ-80A..MZ2200) Floppy Disk Controller |  |

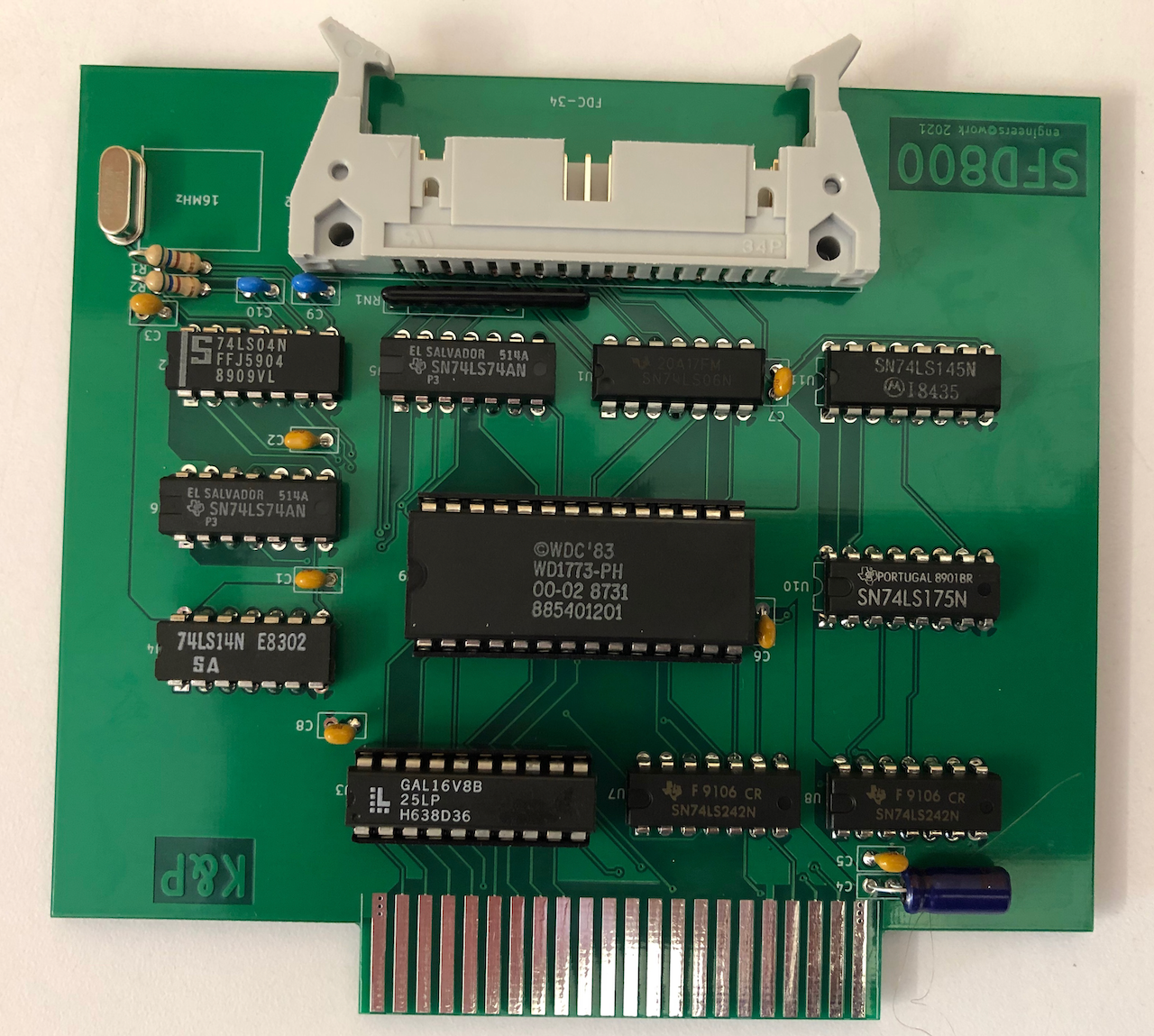

K&P SFD-800 | A recreation of the K&P Floppy Disk Controller | ||

|

Sharp MZ Series | FPGA based hardware emulation of venerable Sharp Business Machines. |  |

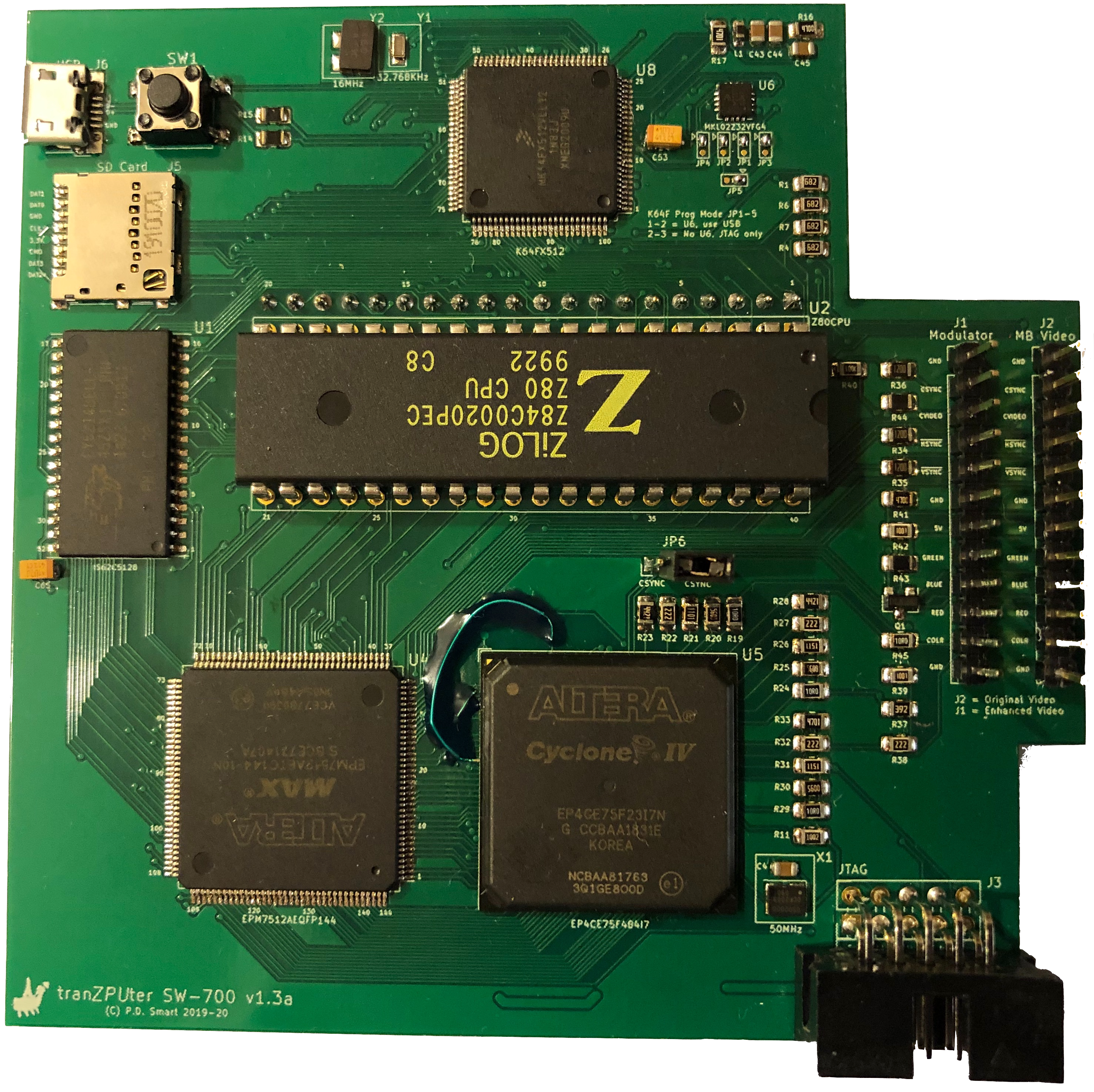

tranZPUter SW 700 | FPGA Accelerator and Video Enhancement for the MZ-700 | ||

|

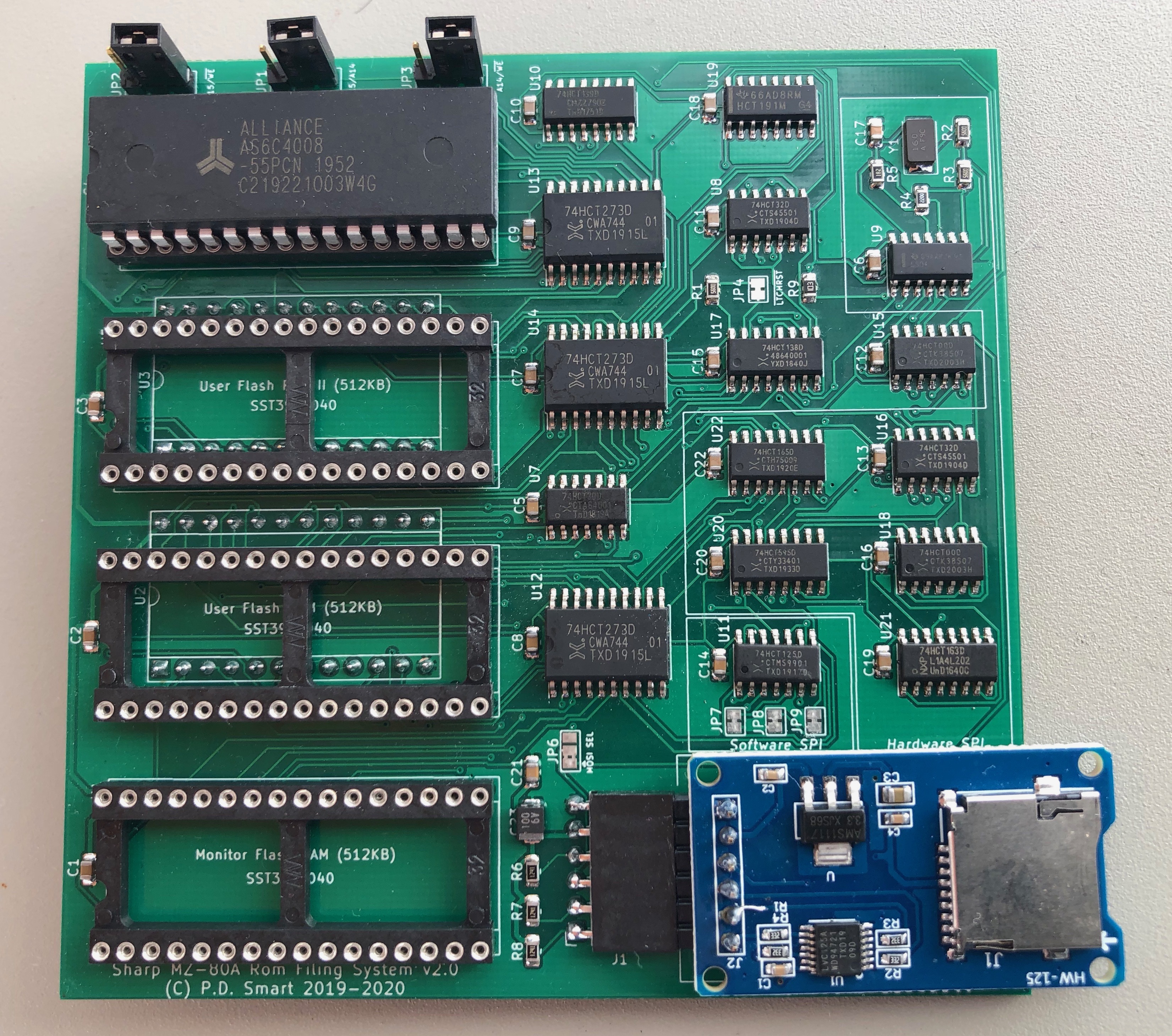

Rom Disk | MZ-80A Rom Disk Board |  |

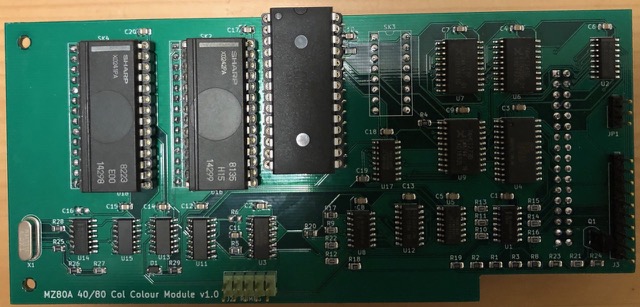

Video Module | MZ-80A 40/80 Column Colour Video Expansion Board | ||

|

zSoft | z-Operating System & Applications |  |

CP/M v2.23 | CP/M for MZ series machines | ||

|

TZFS | tranZPUter Filing System |  |

RFS | Rom Filing System |

Project Information

Active Projects (Last updated: 7th March 2026)

| Project | Date | Status |

|---|---|---|

| picoZ80 | 07/03/26 | picoZ80 v2.5 PCB assembled and operational. RP2350B firmware v3.009 running on Sharp MZ-700 with MZ-700 persona including floppy (WD1773), QuickDisk, RFS, and banked RAM/ROM drivers. ESP32 web interface fully functional. TZFS integration in progress. |

| 01/03/26 | v2.5 boards received from PCB fab, assembled and initial firmware loaded. PIO bus interface verified cycle-accurate on MZ-700. Web management interface operational over WiFi. | |

| pico6502 | 07/03/26 | pico6502 v2.2 PCB design complete. RP2350B firmware adapted from picoZ80 with 6502 PHI1/PHI2 PIO bus interface. Initial bring-up testing in progress. |

| tranZPUterFusionX | 13/05/23 | FusionX now runs on the MZ-700, MZ-80A, MZ-2000 and partially the PCW-8256. MZ-80A/MZ-700 provide original, RFS, TZFS and Linux Terminal modes, MZ-2000 provides original, 1Z-001M Monitor and Linux Terminal modes. |

| 22/02/23 | tranZPUter SW virtual device added. The FusionX can now run as a tranZPUter SW, running TZFS, 64K CP/M, enhanced BASIC SA-5510, Microsoft BASIC all with disk access commands. | |

| 14/02/23 | Firmware updated and tested on an MZ-80A, changes need to be backported to MZ-700/MZ-2000. Concept of virtual hardware added, first candidate is the MZ-80A RFS Board, MZ-80A operates exactly as though this board was installed. | |

| 08/12/22 | First board built along with 3 daughter boards, initial software written and tested in an MZ-700 and an MZ-2000. Both machines function identically to its original Z80 installed equivalent, see twitter for demo’s. Stage 1 on-going, to enable interrupt processing allowing use of CP/M and interrupt based applications. Testing also to be made in an MZ-80A. | |

| 10/09/22 | A Linux based hardware/software concept replacing the Z80 with a dual-core ARM 1.2GHz CPU and GPU running Linux. Aided by hardware for exact Z80 bus timing, the Z80 is instantiated within a Kernel driver under Linux. Design allows for a mainly software solution to upgrading vintage Z80 based hardware. Design and PCB complete and manufactured, awaiting components. Software development on-going via SOM development board. | |

| tranZPUterFusion | 14/02/23 | Boards arrived x10, very expensive, parts sourced, just need a free day to assemble! |

| 10/09/22 | Next generation of the tranZPUter hardware and software concept. Z80 is replaced with an FPGA as per the original concept but includes the I/O processor and 200MHz memory for the ZPU and graphics. Design and PCB complete, waiting for feedback from the tranZPUterFusionX prior to manufacture as the PCB is 5x cost. | |

| zSoft | 13/02/22 | Further updates as the emuMZ and OSD module develop and mature. |

| SharpMZ | 13/02/22 | FDC added for all machines except MZ-80K/MZ-80C which use a non-standard controller. Video Controller enhanced to now render MZ-800 and MZ-2000 video/graphics. Dual SN76489 Sound Generators added along with 24bit DAC’s to allow menu controlled volume. Sound for all machines now routed through sound module and MZ-700 update made to allow sound output from internal speaker. Lots of overall improvements including MZ-2000 host keyboard mapping to allow the Sharp Series to be hosted inside an MZ-2000. |

| 16/10/21 | Updates to the video controller, bug fixes, frame rendering, fixes to the MZ-80B logic and completed the MZ-2000 Video Controller functionality. | |

| ZPU Evo | 26/08/22 | tranZPUterFusion designed to support latest ZPU version, will update the SDRAM module to Octo PSRAM (8bit per edge, double edge) to provide 32bit datapath accesible in 5ns burst mode which should reduce dependency on cache at 100MHz CPU Frequency. 1K Cache stripe necessary to buffer burst mode data. |

| 06/02/21 | SDRAM bug resolved and work commenced to add a stack cache. Stack cache is necessary for the Sharp MZ-700 based ZPU Evolution as the main memory is 512K x 8bit which requires a 32:8 bit FSM reducing performance by a factor of 6 which the stack cache should alleviate. |

Full Project Status History

| Project | Date | Status |

|---|---|---|

sharpkey  |

17/12/22 | No further developments planned. Internal updates for bug fixes or mappings will be pushed to github. Project is stable and reliable on all hosts. |

| 04/09/22 | Source code placed in github for v1.04 with PC-9801 developments. More code tidying, commenting and firmware build documentation needed. The PC-9801 still needs some work such as mappings and tidying which will be done in dev branch and merged to master as I get time. Please contact me if you have issues compiling and please fork and create pull request for any changes. | |

| 12/08/22 | NEC PC-9801 tested and complete, slowly updating the key maps to support Japanese keyboard Sanwa SKB-L1N with correct Kana/Hiragana/Romaji mappings. | |

| 22/06/22 | Bluetooth complete, restructured so that WiFi starts via a reboot. Bluetooth and WiFi cannot coexist easily, both in hardware and ESP API. MZ-5600/MZ-6500 and NEC PC-9801 complete awaiting machines for testing, new keyboards added, User Manual and Technical Guide updated. | |

| 02/06/22 | MZ-5600/MZ-6500, NEC PC-9801 and Bluetooth modules advancing. Brief testing on my MZ-6556, more work to be done once the machine is renovated. Waiting on arrival of the PC-9801 which I originally bought to add a PC-9801 LAN card into my MZ-2800, I used to see this machine and the PC-8801 on-sale in Akihabara and looking at the spec and massive amounts of software available, definitely a machine I will add to my permanent collection and use. | |

| 27/05/22 | Initial version of Technical Guide written. Project published on github with release v1.02. Further updates made to code base and debugging. | |

| 14/05/22 | Version 1 of the multi-input (PS/2 keyboard/mouse and Bluetooth Keyboard/mouse) multi-host (MZ-2500, MZ-2800, MZ-5600, MZ-6500, X1, X68000, NEC-9801, Sharp Mouse) IoT web enabled HID Interface released. Initial draft of the User Manual written, technical documents to follow. | |

| x1key | 02/06/22 | This project fully works and stable with the tweaked firmware from Kyouchi Sato, no further developments to be made with the advent of the SharpKey |

| 13/02/22 | X1 PS/2 Keyboard Interface. New project under way to interface a PS/2 keyboard with an X1 Turbo using an existing design based on a Renesas R8C processor. The project takes the original authors prototype and makes a more formal end-user friendly product. | |

| mz25key | 02/06/22 | SharpKey firmware now adapted to the mz25key and can be build time targeted at an MZ-2500, MZ-2800 or if a small modification is made, allow full SharpKey host detection and configuration. This project is now officially stable and frozen. All new developments are made under the SharpKey project. |

| 03/03/22 | Finally finished the MZ-2800 version of the interface which needed a socket replacement in the main machine as plugs for the old socket are no longer obtainable. | |

| 20/02/22 | Completed protocol and mapping for the MZ-2800 keyboard. The firmware is build time selectable between the MZ-2500/MZ-2800 as the timing is different and didn't want to add extra logic to cater for two protocols as it would affect timing. Found a suitable replacement for the MZ-2800 9pin AMP connector, mounted it and just waiting for the matching plug which was on backorder. Tested the interface in both MZ-2500/MZ-2800 modes and works fine, even playing games such as Galaga. | |

| 13/02/22 | MZ-2500/MZ-2800 PS/2 Keyboard Interface. New project just completed to interface a PS/2 keyboard with an MZ-2500/2800 using an Espressif ESP-32 SoC all wrapped up in a tiny KM-24 case. | |

| MZ-80A Video | 11/04/21 | Version 1.1 board tested and 5 assembled. External Horizontal Sync seen to have an artifact which is under investigation prior to board release. |

| 24/03/21 | New v1.1 board assembled and currently undergoing testing. | |

| 18/02/21 | Update, corrected outstanding issues, use a multivibrator to ensure no write to attribute RAM when control latch updated, fixed PCB design issues with v1.0 | |

| 29/07/20 | Bug fixes and testing with the RFS v2.0 board alongside the tranZPUter v1.1 and v2.1 boards. Commands and features added. | |

| 04/09/20 | V2.0 Initial CPLD/FPGA coding complete, video module fully working for MZ-80A (K/C/1200) and MZ-700, needs to be tested for MZ80B albeit hardware defined and running. 640x200, 8 colour pixel graphics added keeping in-line with the SharpMZ Emulator. Ability to overclock MZ-80A motherboard now allows the MZ-700 mode to run at 3.54MHz and the MZ80B mode to run at 4MHz. | |

| 15/08/20 | PCB assembled, initial JTAG and boundary tests made, now forwarding the VHDL to instantiate the required video controller functionality. | |

| 24/07/20 | PCB arrived and awaiting parts so I can assemble it, in the meantime work on the VHDL required for the FPGA has started. | |

| 04/07/20 | Version 2.0 designed and PCB ordered. In order to shrink the size and provide functionality so that an MZ-80A can run and display software from other MZ Series computers the video now uses a CPLD and an FPGA. Their is synergy with the Sharp MZ Emulator and an eventual convergence. | |

| 23/8/19 | Version 1.0 is reliable but I want to correct the control register access such that a write to the last bytes of attribute RAM doesn't occur when changing PCG bank or switching between 40/80 col. | |

| tranZPUterSW-700 | 26/08/22 | Future tranZPUter development will be made with the Fusion devices. This platform is stable and small updates will be made for internal use. The tranZPUterFusion is the successor to this device. |

| 13/02/22 | Major advances with the Sharp MZ Series FPGA clone. Floppy disk controller now added, MZ-800 mode added, MZ-2000 mode added and general feature enrichment. The tranZPUter SW-700 has been ported to an MZ-2000 and an MZ-80A providing both with all the enhanced capabilities bestowed on the MZ-700. Both machines use an unmodified tranZPUter SW-700 board with an adapter to interface the mainboard, CRT and sound. Grey scale approximation circuit added so colour now appears in shades of green. Please bear with me on documentation as I haven't got around to making updates for quite some time! | |

| 16/10/21 | Created a CPLD version specific to the MZ-2000 so that a tranZPUter SW-700 board functions inside an MZ-2000 host. Updated the Video Controller to provide full MZ-2000 GRAM capabilities and some changes such as just in time frame rendering. MZ-2000 requires a small daughter card to allow interception of the internal monitor and sound signals. Internal monitor can now display distinct grey signals for colour. | |

| 25/07/21 | Updated TZFS to allow it to read/write all MZ Series machine cassette formats. The SD <–> Tape and Bulk conversion tools also updated. | |

| 17/07/21 | Ongoing updates to the Sharp MZ Series emulation v2.0 on the tranZPUter SW-700 board. OSD hardware and software now mostly written, base emulation hardware ported but still more to do. | |

| 15/06/21 | Major VHDL updates, porting the Sharp MZ Series logic into the tranZPUter which involves on the MZ-700 side: writing bus arbiters, interrupt generators, keyboard processors, dual real/virtual CMT interface and extending the video controller to support OSD status and menu buffer. Modularising and updating the Sharp MZ Series clone logic so it is more portable and cleanly supports an IO processor. | |

| 20/04/21 | Updated BASIC SA-5510 to handle SD card storage/query and more minor bug fixes. | |

| 03/04/21 | Version 1.3 bug fixes, located and corrected a major bug introduced from the v1.2->v1.3 migration. | |

| 20/12/20 | Version 1.3, initial PCB errors but now running soft CPU’s in the FPGA, the original tranZPUter concept is being achieved. With the bigger FPGA, the design now allows the use of a soft T80 and the ZPU (with space for many more). Work is currently underway to finetune the ZPU and zOS which runs native on the MZ-700 console. Repository will be updated once I'm happy I’ve achieved Alpha status. | |

| 17/11/20 | Version 1.2 running well and stable. Separate branch created in GIT for hardware and software as this will develop along different lines compared with v1.3. | |

| 08/11/20 | The latest addition to the tranZPUter line, the tranZPUter SW-700, an amalgamation of the tranZPUter SW v2.2 and the Video Module v2.0 on a single daughter board for installation into a Sharp MZ-700. The board has been designed, built and tested with a significant portion of the VHDL, Z80 and C code written. | |

| tranZPUterSW | 24/03/21 | Updates to the CPLD HDL, bringing in developments from the tranZPUter SW-700 and adding a new MZ-800 memory management mode to allow MZ-800 host compatibility. |

| 08/11/20 | v2.2 been developed in tandem with the tranZPUter SW-700 board. This board operating with the Video Module v2.0 are now proving quite stable. Still a few more niceties to add and no doubt bug fixes. | |

| 04/09/20 | v2.2 built and debugged, required the addition of a reset line on the JTAG port to allow SWD programming. Both Teensy version with bootloader MCU and non-Teensy version programmed via the OpenSDA adapter on the FRDM-K64F development board work as expected. Test programs run on the K64F, zOS tested and SD card verified, all work as expected, now needs updates to zSoft for the pin changes due to different version of the K64F being used (ie. TQFP-100) to complete, WIP. | |

| 15/08/20 | v2.2 designed and PCB submitted for manufacture. The Teensy 3.5 has been removed from the design due to complexities in assembly and replaced with a 100pin QFP MK64FX512 MPU with the option to install the Teensy bootstrap MCU if required, otherwise all programming is now made via the JTAG interface. | |

| 29/07/20 | v2.1 updates, CPLD more robust and supporting multi frequency and MZ-700 mode, software updates, both basic and K64 enhanced versions tested with RFS and TZFS. A few more user and saturation tests, a new PCB cut to add the external oscillator facility on basic boards and a new separate layout board for the MZ-700 and the tranZPUterSW is production ready. Future development will be on the FPGA based tranZPUter | |

| 24/07/20 | v2.1 board assembled (x6), issues with the PCB which oxidized and excreted resin, but managed to get 4 working boards out of a total of 6 made. CPLD VHDL has been coded and working, compatible with version 1.0->2.0 and adds hardware compatibility for the MZ-700. Time spent trying to add MZ-80B compatibility but insufficient resources in the CPLD for the requirements. At least the MZ-80B mode allowed fine tuning of a write back mechanism where the CPLD could intercept a transaction, tri-state the Z80, update the hardware and re-enable the Z80. | |

| 04/07/20 | v2.1 designed with a 512 macro cell CPLD and additional changes as the list of features needed to be fulfilled grows. v1.1 is a stable discrete logic version of the project for anyone seeking to upgrade a Sharp MZ-80A to use an SD card, faster processor, more memory and some compatibility with other models such as the MZ-700 | |

| 26/06/20 | Design updated to v1.1 and new PCB designed and ordered. V2.0 is under way using a CPLD to decrease size and add ability to easily add required features (such as MZ80B virtual hardware). | |

| 18/06/20 | Hardware updated to support WAIT state generation on IO commands. This now allows the MZ-700 software such as S-BASIC to run. Added Microsoft (NASCOM) Basic in two flavours, original MZ-80A and tranZPUter variants with updated commands to access the SD card and a converter program to convert NASCOM tape images. Star Trek V2 running at 10MHz under Microsoft BASIC with the inbuilt ANSI Terminal Emulator is now much more playable. | |

| 10/06/20 | MZ-700 mode needs hardware assistance on memory bank switching, even over clocking the K64F at 168MHz it still misses the odd Z80 IORQ timing requirement due to other IRQ events such as the thread library. Patched the 1Z-013A MZ-700 BIOS to use the MZ-80A keyboard and adjusted the colour attribute RAM, so almost ready to run MZ-700 software on the tranZPUterSW. Completed the multi-frequency option for the Z80, it now clocks at 9MHz reliably on the Z80H CPU which makes CP/M fly!! |

|

| 07/06/20 | Adding the MZ-700 mode is proving more tricky, written ARM assembly ISR routines but the K64F isn't as fast as I had presumed. Example, highest priority interrupt on IORQ with just two register pushes and a bit toggle only just meet the Z80 timing to add a wait state. WIP!! Documentation slowly being updated. | |

| 04/06/20 | TZFS written (TranZputer Filing System) and CP/M ported and CBIOS written, result is actually better than the MZ-80A_RFS and more developments planned. Documentation to be updated shortly. | |

| 19/05/20 | Development underway, tools written to create the decoder flashram map, tools written for zOS, can load, save and manipulate all the memory on the tranZPUter SW board and on the Sharp MZ-80A host from zOS, base library coded for K64F access to the Z80 host and tranZPUter board in C | |

| 13/05/20 | tranZPUter SW v1.0 PCB fully assembled and tested. Software development now underway. | |

| 09/04/20 | Parallel project to the tranZPUter, designed the hardware and PCB, readying zOS to use with this project. | |

| zSoft | 16/10/21 | Updates to allow zOS to operate inside an MZ-2000 on the tranZPUter SW-700 board. |

| 15/07/21 | Major updates to allow the K64F to act as the initial IO processor for the Sharp MZ Series emulation. This logic is being developed so it easily compiles and works with the ZPU Evo, the intended standalone IO processor within v2.0 of the Sharp MZ Series Emulator in the MiSTer project. | |

| 24/03/21 | Additions to support the MZ-800 which utilizes the tranZPUter v2.2 board. Some bug fixes introduced while working on the FPGA Soft Processors now resolved. | |

| 18/02/21 | Update, corrected outstanding issues, use a multivibrator to ensure no write to attribute RAM when control latch updated, fixed PCB design issues with v1.0 | |

| 20/12/20 | A lot of ongoing changes to accommodate v1.2 and the newer v1.3 tranZPUter SW-700 boards. With the advent of the ZPU in the design, zOS needs to be compiled as an embedded OS and as a user OS driving keyboard/screen directly along with storage and ability to run applications. A lot of possibilities exist, currently on with the framework. | |

| 08/11/20 | Updates to accommodate the tranZPUter SW-700 v1.2 board. | |

| 05/09/20 | Updates to accommodate the tranZPUter v2.2 board. Separate developmnet branches now created for v2.1/2.2 as both boards are in use but differ in certain aspects. | |

| 18/06/20 | Further updates for NASCOM BASIC and the MZ-700 mode with the new hardware | |

| 18/06/20 | Further updates for NASCOM BASIC and the MZ-700 mode with the new hardware | |

| 10/06/20 | Further updates to accommodate TZFS, CP/M and MZ-700 mode running on the tranZPUter SW board with multi-frequency switching. | |

| 19/05/20 | Bug fixes to zOS as it gets used for the tranZPUter SW project. Tools and libraries written for the tranZPUter SW to utilise the new board and to provide a platform to port RFS to the tranZPUter. | |

| 12/05/20 | Major changes. I decided to adopt more standard C Libraries especially as the K64F ARM compiler and libraries were difficult to use without libc, so I’ve added umlibc for the ZPU and removed the El Chan xprintf library. Also standardised memory management, the OS manages its heap and applications generally call on the OS for memory allocation but I've kept in place the framework for an application to have its own memory management if needed. | |

| 28/04/20 | Merged IOCP, ZPUTA, zOS and Applications from ZPU Evo and tranZPUter repositories. All software for the two projects will be made in this repo. | |

| MZ-80A RFS | 11/04/21 | Updated CPM, removed CP/M ROM and RAM Drives as they offered no real benefit over the hardware SD as it clocks at 1MB/s allowing for 4x16MB SD Drives + 2xFloppy Drives. Updated Microsoft BASIC to use RFS SD card, creating 4 distinct compile time versions enroute. |

| 03/04/21 | Updated RFS for HW v2.1 board, bug fixes and to provide 10 RFS Drives on an SD card. Modified BASIC SA-5510 to allow load, save and dir listing of files on an SD card. | |

| 24/03/21 | New v2.1 board assembled and currently undergoing software update/testing alongside the Video Module v1.1. | |

| 18/02/21 | Update, added the additional components deemed necessary in v2.0 design which were reworked onto the PCB and cosmetic changes to PCB layout. | |

| 29/07/20 | Bug fixes and testing with the RFS v2.0 board alongside the tranZPUter v1.1 and v2.1 boards. Commands and features added. | |

| 14/05/20 | New PCB assembled, tested and the RFS and CPM CBIOS software updated. The Hardware SPI gives almost Flash RAM performance and is ideal for CPM use. A minor tweak to the hardware was needed due to the CSUSR signal being activated as an artifact of the 82S100N configuration on the main motherboard and R2 was removed given the choice of XTAL, but otherwise all as designed. | |

| 02/04/20 | New version of the hardware and PCB design based on enhancement of the shortcomings of version 1.1. v2.0 schematic , v2.0 pcb. | |

| 24/03/20 | More major changes, added an SD card to the design, updated the RFS to access Sharp MZ-80A programs on the SD card and also updated CPM so that it can access the SD card as a set of virtual 16MB fixed drives. | |

| 25/02/20 | Major changes as I have implemented CPM and wrote the CBIOS / Ansi Terminal Emulator in the banked Rom. Currently beta level, CPM boots and runs fine, just the keyboard mappings need enhancing and some tweaks to the Ansi Terminal Emulator. Currently adding an SD Card into the hardware design and will add the software shortly thereafter. | |

| 23/8/19 | Version 1.0 of the hardware and software are reliably running but I'm in process of making a v1.1 PCB with corrections and additional logic to enable writing by the MZ-80A to the Flash RAM. | |

| SharpMZ | 02/06/22 | No future updates planned for MiSTer project. SharpMZ Series FPGA Emulation will only be available on the tranZPUter project boards. |

| 17/07/21 | v2.0 - Decided to rewrite the OSD logic (ie. not use the MiSTer version) to keep to the zSoft methods. Most of the framework now written which can be seen on the website v2.0 tranZPUter SW-700. v1.0 - Alan Steremberg has kindly updated the hardware to use the new HDMI IP and Scaler allowing the MiSTer version to run with HDMI as well as VGA. |

|

| 15/06/21 | Major logic changes to make the Sharp MZ Series logic more modular and portable, initial target being on the tranZPUter SW-700 card but all the updates will be migrated to the MiSTer core once complete. | |

| 30/4/20 | Placed one of the latest dev versions into gitlab/github and updated the Main_MiSTer code due to file handling changes made by collaborators. | |

| 30/4/20 | Placed one of the latest dev versions into gitlab/github and updated the Main_MiSTer code due to file handling changes made by collaborators. | |

| 7/6/19 | Many fixes and updates have been made compared to the MiSTer_Devel released version 1.0 and started to add an IOCTL module so that the ZPU Evo can be embedded and take control of the emulator hardware. IOCTL is how MiSTer_Devel allows the HPS to control the target emulator so I’m keeping this mechanism in place for consistency. | |

| tranZPUter | 06/09/20 | Version 2.0 designed and PCB well under way. I hit upon new ideas during the PCB layout and commenced v2.1 of the design so v2.0 may not be manufactured. |

| 24/03/20 | Debugged the hardware and made changes resulting in v1.1a of the hardware design. Slowly working out the FSM in VHDL to read/write between the FPGA and the Z80 Host. Also still waiting on me going Eureka and finding the bug in the L2 to L1 cache when using SDRAM!!! | |

| 15/12/19 | Updated with the new ZPU Evo core and working SDRAM controller, 48K BRAM and 4MByte SDRAM so external applications can run (needed as main transZPUter app will run in SDRAM and more BRAM will be allocated to cache). | |

| 23/9/19 | Waiting on the ZPU Evo. Hardware designed, tested and test ditties written to check that the FPGA can Master the Z80 Bus and utilize it’s hardware. Started the software (in C) framework based on the SharpMZ Emulator code. | |

| ZPU Evo | 28/01/20 | The SDRAM, both vanilla and cached versions (1 row per bank cache) are working and pass all the memory tests at 100MHz. Unfortunately when using the SDRAM for program execution it highlighted a bug in the ZPU Evo which I have been trying to resolve. The bug is timing related and is between L2 to L1 and only shows up due to the timing delay of SDRAM. Using the cached SDRAM the bug is not so frequent but it needs resolving as the transzputer project needs SDRAM for applicaiton execution. To be resolved shortly! |

| 28/01/20 | The SDRAM, both vanilla and cached versions (1 row per bank cache) are working and pass all the memory tests at 100MHz. Unfortunately when using the SDRAM for program execution it highlighted a bug in the ZPU Evo which I have been trying to resolve. The bug is timing related and is between L2 to L1 and only shows up due to the timing delay of SDRAM. Using the cached SDRAM the bug is not so frequent but it needs resolving as the transzputer project needs SDRAM for applicaiton execution. To be resolved shortly! | |

| 23/12/19 | Replaced megacore dual-port BRAM used for L2 cache with inferred RAM to aid in portability and updated write-thru to work at byte level (for self modifying code). Found and corrected a byte/half-word write bug which always defaulted to read-update-write. Changed the multiplication logic to meet timing (use of variable/combinational logic was causing significant negative slack impact). Fixed the timing for L2 Cache access. SDRAM now working for Wishbone and system bus reliably at 75MHz and meeting timing constraints. Still having issues running reliably > 75MHz no matter how the timing is arranged, still a work in progress. Used Signal Tap but cannot see reason. Still to add Burst mode for L2 Cache from SDRAM, design worked out using BRAM just have to code it. | |

| 31/10/19 | The ZPU Evo is complete, I would say at Beta status until it is fully running in the SharpMZ project when I will stress it and add extra instructions. Debugging the WishBone SDRAM Controller, adding burst mode for L2 Cache Fill. Once the SDRAM Controller is fully working progress can be made on it’s dependents, for example the tranZPUter uses the Cyclone 10LP which has limited BRAM memory but an external 8M SDRAM chip so the SDRAM Controller is currently a showstopper. | |

| dPWR | 12/11/19 | dPWR has been running reliably for 4 years, it needs tidying up a bit in terms of instructions, user guide and howto program additional modules/devices. |

| jDPWR | 16/11/19 | I started to write this Java version based on dPWR two years back but it got sidelined when I started the VHDL projects. I will finish it but no definite date yet. |

Project Dependencies

| Project | Dependents | Notes |

|---|---|---|

| ZPU Evo | tranZPUter | The tranZPUter uses the ZPU Evo as it’s primary soft processor |

| ZPU Evo | SharpMZ | The SharpMZ Emulator will have the ZPU Evo embedded to act as the IO and User Interface processor making the project less dependent on FPGA resources such as the embedded HPS on the Cyclone V. |

Bug Tracking

| Project | Ticket # | Date | Status |

|---|---|---|---|

| CP/M | A000001 | 26/02/20 | Ansi emulation not recognising clear screen. |

| A000002 | 26/02/20 | ||

| A000003 | 28/02/20 | ||

| MZ-80A RFS | B000001 | 23/08/19 | |

| ZPU Evo | C000001 | 28/01/20 | |

| tranZPUter | D000001 | 28/02/20 | |

| SharpMZ | E000001 | 22/04/20 | |

| dPWR | F | ||

| jDPWR | G | ||

| MZ-80A Video | H000001 | 23/08/19 | |

| tranZPUterSW | I | ||

| tranZPUterSW-700 | J |

Background

This is a collection of our open source projects, system renovations and technical information, most of which is freely available via the Open Source framework using the GNU Public License v3* for non-commercial use.

The documentation on this site tends to start off as an information dump with grammatical errors due to the rapid development nature of the projects and then over time will become more professional, rounded and complete. Please re-visit regularly if any project is of interest to you to obtain updated documentation.

* Strictly no commercial use of these projects unless agreed in writing.